## FlowPix: An Image Processing DSL based on an FPGA Overlay Accelerator

## Abstract

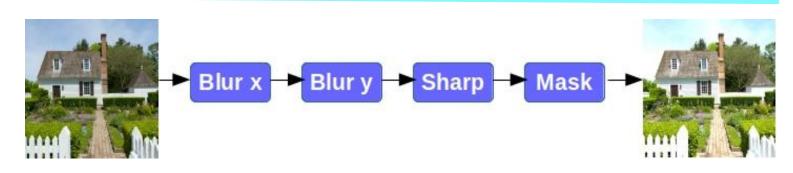

Figure: Unsharp Mask pipeline.

- An image processing pipeline can be viewed as a graph of interconnected stages that processes images successively.

- Image processing algorithms have high spatial and temporal parallelism which makes them favourable for FPGA implementations.

- We propose an overlay based framework to realize image processing algorithms on FPGAs.

- The major goal is to ease programming effort through a DSL, enabling programmers to use FPGAs as target devices.

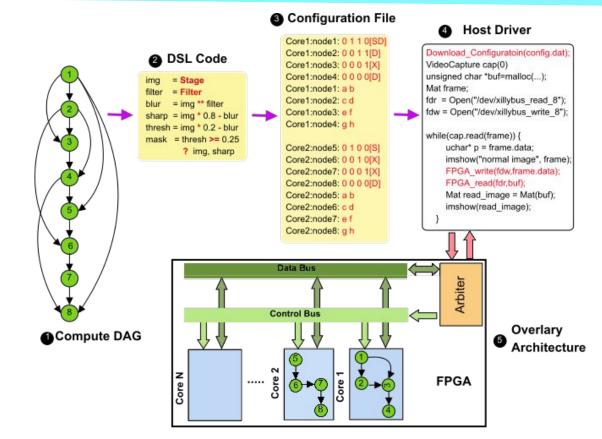

## Hardware Architecture

## Fig 2. Overall block diagram of our framework.

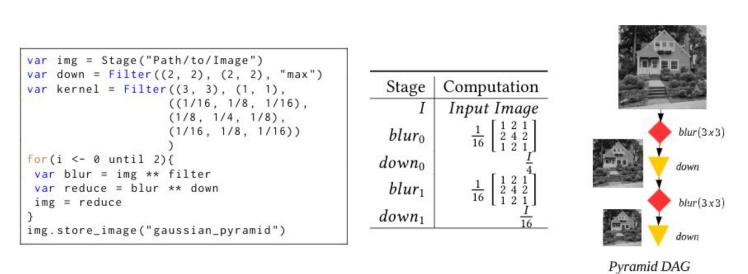

Fig 3. FlowPix DSL code for a two stage pyramid.

Authors: Zlaul Choudhury, Anish Gulati, Shashwat Khandelwal, Suresh Purini

# R&D SH WCASE 2021

### **Technology, Social Impact**

## **Evaluation**

LOCAL LAPLACIAN

HARRIS CORNER DETECTION

CANNY EDGE

## Figure. Few image processing algorithms accelerated by our overlay.

| Benchmarks               | #cycles | Latency | FPS | PR   |

|--------------------------|---------|---------|-----|------|

| Canny Edge               | 1044484 | 8.35ms  | 119 | 1.00 |

| Harris Corner detection  | 1040399 | 8.32ms  | 120 | 1.00 |

| Multiscale interpolation | 1024143 | 8.19ms  | 122 | 3.94 |

| Unsharp Mask             | 1044483 | 8.35ms  | 119 | 1.00 |

| Sobel                    | 1044484 | 8.35ms  | 119 | 1.00 |

## Computer Systems Group

)3 03 03